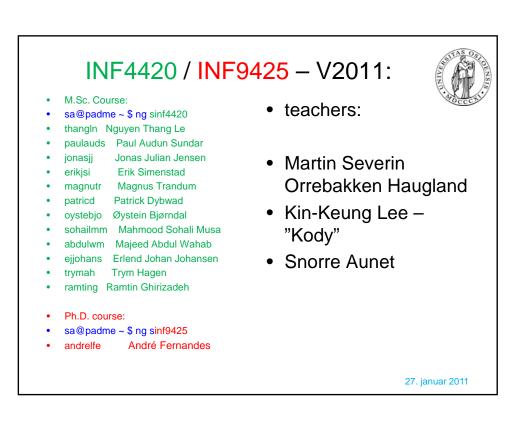

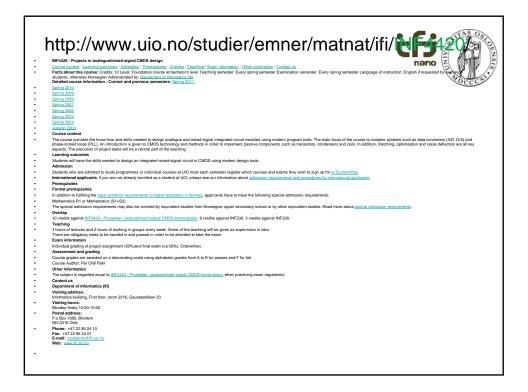

## INF4420 / INF9425 INF4420 - Projects in analogue/mixed-signal CMOS design

Snorre Aunet (sa@ifi.uio.no) Nanoelectronics group Department of Informatics University of Oslo

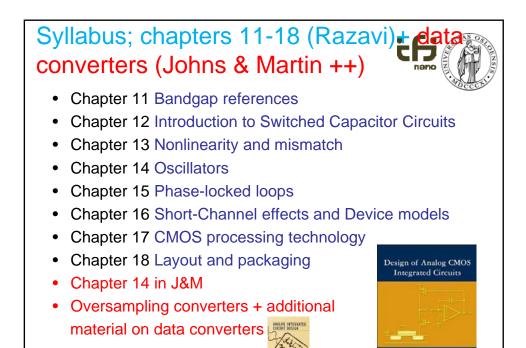

|       |           | INF4420 / INF3410                       |     |

|-------|-----------|-----------------------------------------|-----|

| 11 Ba | andgap Re | ferences                                |     |

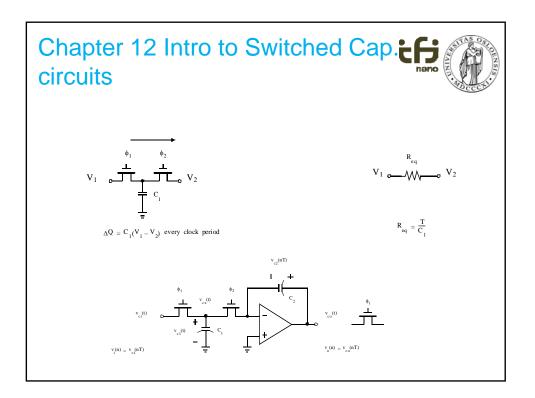

|       |           | n to Switched-Capacitor Circuits        |     |

|       |           | y and Mismatch                          |     |

|       |           | ,                                       |     |

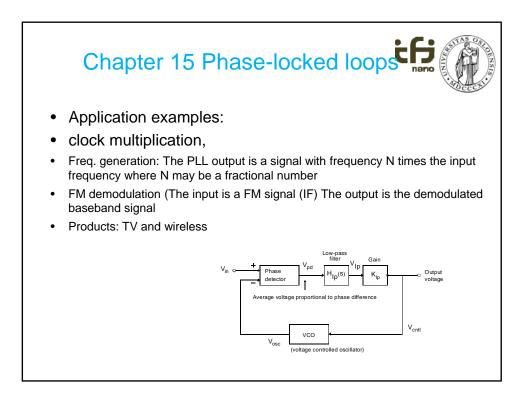

|       |           | ed Loops                                |     |

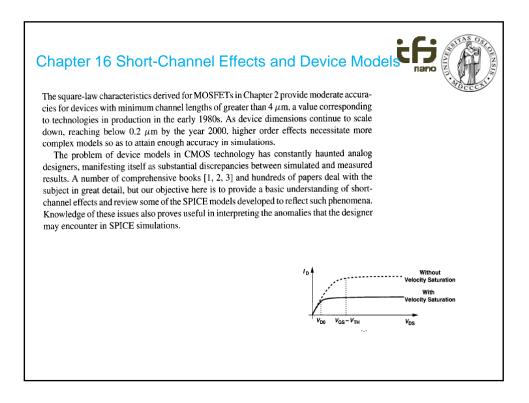

|       |           | nel Effects and Device Models           |     |

|       |           |                                         |     |

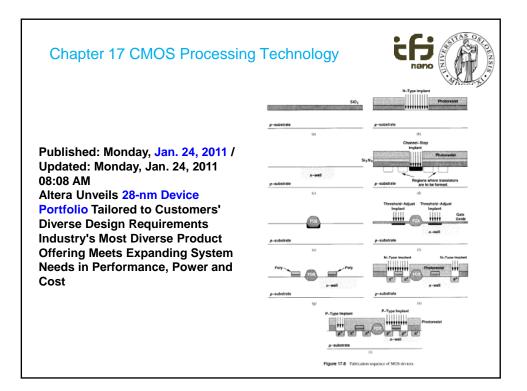

|       |           | cessing Technology                      |     |

|       |           | Packaging                               |     |

| In    | dex       |                                         | 677 |

|       | 1         | Introduction to Analog Design           | 1   |

|       | 2         | Basic MOS Device Physics                | 9   |

|       | 3         | Single-Stage Amplifiers 4               |     |

|       | 4         | Differential Amplifiers                 |     |

|       | 5         | Passive and Active Current Mirrors      |     |

|       | 6<br>7    | Frequency Response of Amplifiers        |     |

|       | 8         | Feedback                                | -   |

|       | 9         | Operational Amplifiers                  |     |

|       | 10        | Stability and Frequency Compensation 34 |     |

|       |           |                                         |     |

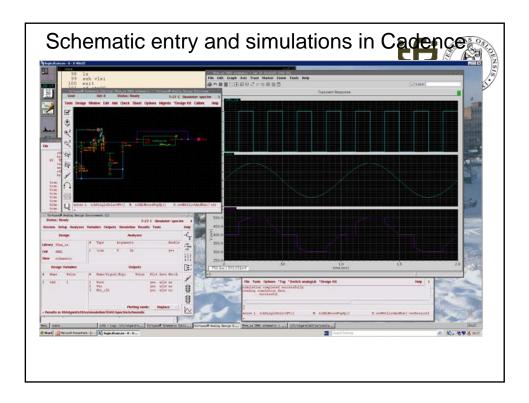

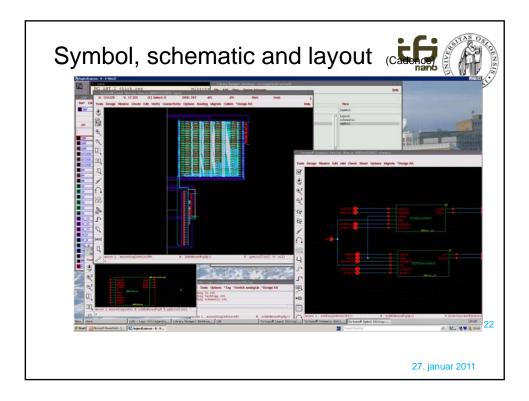

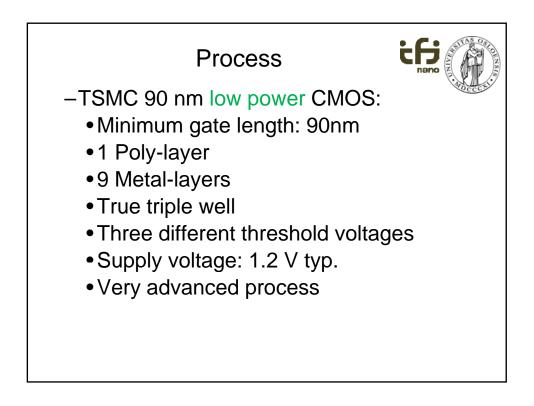

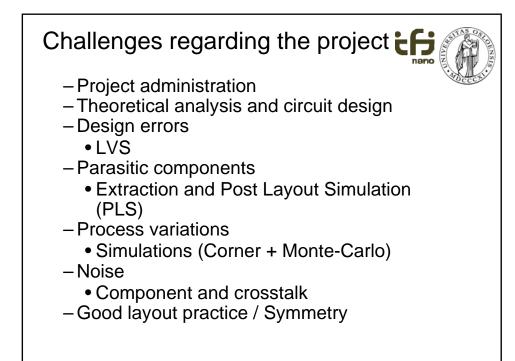

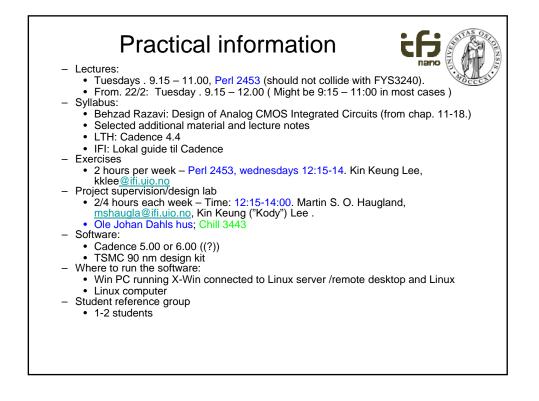

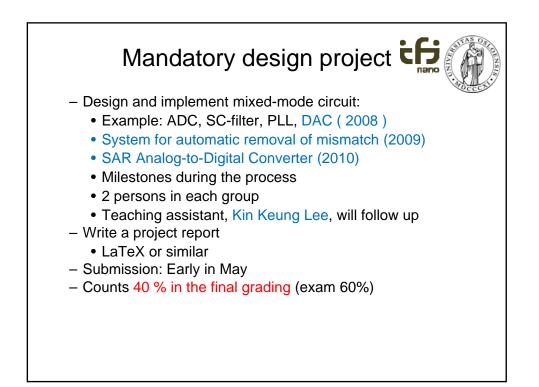

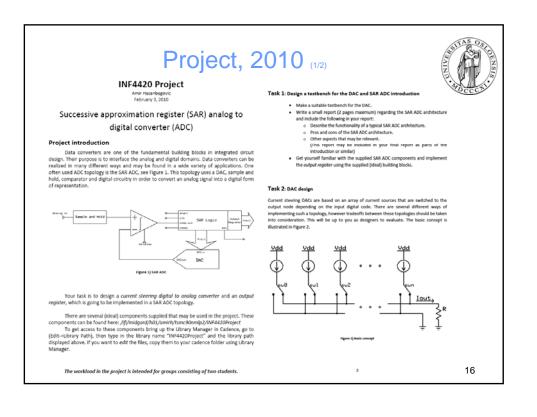

## Project, 2010 (2/2) si When you have completed the ry ou have completed the layout, run Design Rule Check (DRC) and Layout z schematic (US). These checks have to be free of errors. The LVS output log be included in the final report as an appendix. the first this DAC and Minimum Bbit resolution Sample rate > 8Ms/s DNL < 4/- 0.5138 Hinimum output signal range of 60DmV. ().e 0-60DmV Minimum output signal range of 60DmV. ().e 0-60DmV The next step is to do back annotation of parasitic components (R and C) to the schematic view, or parasitic extraction as it is also called. This will result in a netlist with parasitic resistances and capacitances. ular implementation the supply voltage is 1.2V and you may assume you have a 1uA available for biasing. 5) On the basis of the extracted netlist, you may now do post layout simulations (Monte Carlo simulations included). Her you must carry out the appropriate simulations and compare them with the previous simulation results that were solely based on the schematics. e several other DAC specifications that are important, such as po Identify these specifications and include them in your final report Task 3: Implementation of DAC into SAR ADC **Report requirements** lement your DAC design into the SAR ADC topology. Make necessary modifications to the il components if your implementation has higher specifications then the minimum (for mple resolution). The final report may be written it the text editor of your choice, but the report must be well organized and easy to read. All exercial aspects of the project must be supplied by relevant figures and plots. It is important to document/justify the choices you make regarding both the schematic and layout, (important topics may be matching, transitor dimension, choice of components etc.) Nots of all the schematics and the layout, with clearly visible parameters such as dimensions must be included as an appendix for all circuity/ub circuits. References that you may have used in the project must also be included. All schematics and layouts must be made available for inspection, with the east directory path specified in your final report. Everything must be understandable just from reading the final report. Assign a ramp up signal to the ADC input and verify that you get corresponding digital values on the ADC output. Project requirements sup members must jointly go through the project description and assign work gromens. It must be made vusible in the report how the distribution of work has been goed throughout the project. The following (*but not limited* to) tasks must be addressed or the project can be regarded as complete: Submissions and approvals Task 1. Mandatory hand-in. Schematics (approved by lab advisor) Deadline February 15. It is expected that all circuits/sub-circuits have a schematic and appropriate symbol Task 2. Schematic (approval by lab advisor) Deadline March 15. Schematic (approval by lab advisor) Deadline April 12. The final DAC should be made up of a single symbol. After the DAC schematic is complete and all simulation results (including Monte Carlo simulations) are statisticatory, a layout of the complete system must be made. There are certain issues that are often encountered when doing analog/made-signal layout. Find out what they could be and discribe them in your final report. Make an effort to implement countermeasure. Schematic (approval by lab advisor) Deadline April 12. Layout (approval by lab advisor) Deadline April 12. Task 3. Deadline April 19. Final Report. Deadline May 4.

## ck (DRC) and Layout

17

9