# Bandgap references, sampling switches

Tuesday, February 1st, 9:15 – 12:00

Snorre Aunet (sa@ifi.uio.no)

Nanoelectronics group

Department of Informatics

University of Oslo

### Outline – Tuesday, February 1st

- 11.1 General considerations

- 11.2 Supply-independent biasing

- 11.3 Temperature-independent References 2.46540

- 11.3.1 Negative TC-voltage

- 11.3.2 Positive TC-voltage

- 11.3.3 Bandgap reference

- 11.4 PTAT Current generation

- 11.5 Constant-Gm Biasing

- 12.2 Sampling Switches

- 12.3 Switched Capacitor amplifiers

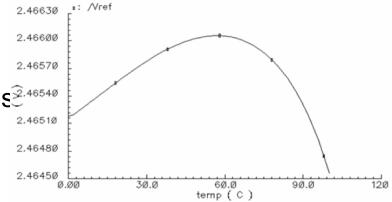

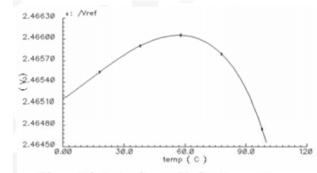

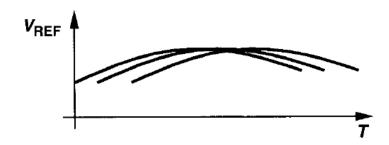

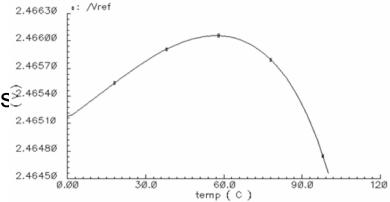

Figure 4 Output reference Verf vs. temperature.

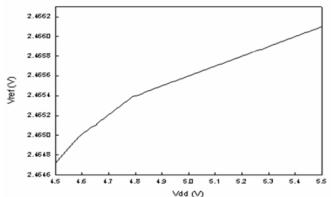

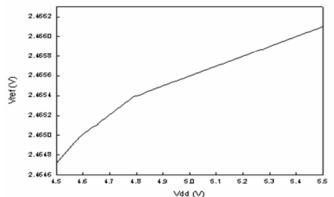

Figure 5 Output reference Vref vs. power supply Vdd.

A High Precision Curvature Compensated Bandgap Reference without Resistors

#### Bandgap references for stable dc quantities

- References that exhibit little dependence on supply and process parameters and a well defined dependence on temperature

- The required temperature dependence assume one of three forms:

- 1) proportional to absolute temp. ("PTAT")

- 2) constant G-m behaviour

- 3) temperature independent

- Design for supply-independent biasing and define temperature variation

**Figure 11.28** A/D converter using a reference generator.

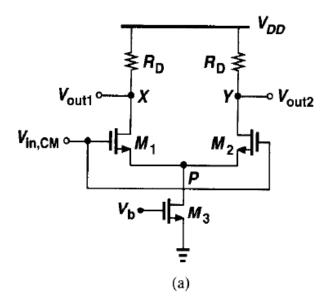

#### 1.2 Supply independent biasing ("Razavi" pp. 377.)

Figure 11.1 Current-mirror biasing using (a) an ideal current source, (b) a resistor.

$$\Delta I_{out} = \frac{\Delta V_{DD}}{R_1 + 1/g_{m1}} \cdot \frac{(W/L)_2}{(W/L)_1}.$$

11.2 Simple circuit to establish supply-independent currents.

A resistor tied between the supply voltage (" Vdd ") and the gate gives a circuit quite sensitive to V<sub>DD</sub> variations.

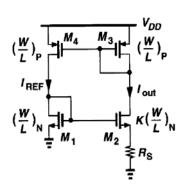

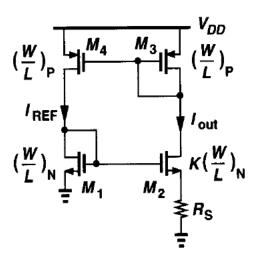

> Less sensitive solution where the circuit bias itself, with I<sub>ref</sub> being a replica of  $I_{out}$  ( $\lambda \approx 0$ )

$$I_{out} = K I_{ref}$$

#### Uniquely defining currents by adding a resistor

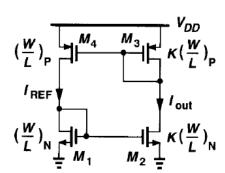

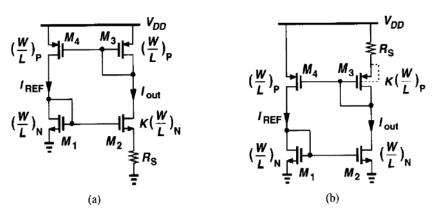

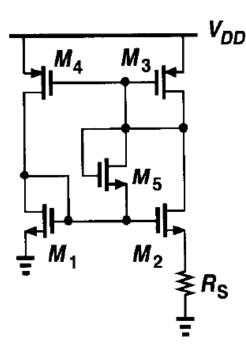

**Figure 11.3** (a) Addition of  $R_S$  to define the currents, (b) alternative implementation eliminating body effect.

require that  $I_{out} = I_{REF}$  because they have identical dimensions. We can write  $V_{GS1} = V_{GS2} + I_{D2}R_S$ , or

$$\sqrt{\frac{2I_{out}}{\mu_n C_{ox}(W/L)_N}} + V_{TH1} = \sqrt{\frac{2I_{out}}{\mu_n C_{ox} K(W/L)_N}} + V_{TH2} + I_{out} R_S.$$

(11.2)

Neglecting body effect, we have

$$\sqrt{\frac{2I_{out}}{\mu_n C_{ox}(W/L)_N}} \left(1 - \frac{1}{\sqrt{K}}\right) = I_{out} R_S, \tag{11.3}$$

and hence

$$I_{out} = \frac{2}{\mu_n C_{ox}(W/L)_N} \cdot \frac{1}{R_S^2} \left( 1 - \frac{1}{\sqrt{K}} \right)^2.$$

(11.4)

- The current becomes independent of the supply voltage (but still a function of process and temperature).

- The assumption  $V_{TH1} = V_{TH2}$  introduces some error, but a simple remedy is shown in Fig. 11.3 b), by eliminating the body effect by tying the source and bulk of each PMOS transistor.

These circuits exhibit little supply voltage dependence if the channel length modulation is neglible → long channels

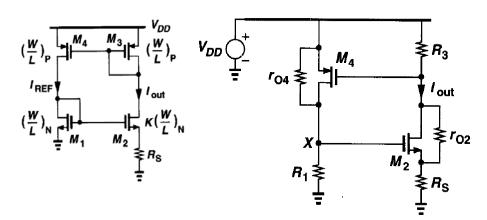

# Ex. 11.1 Estimating the change in $I_{out}$ for a small change $\Delta V_{dd}$ for the BG-ref. in Fig 11.3 a)

#### Solution

Simplifying the circuit as depicted in Fig. 11.4, where  $R_1 = r_{O1} \| (1/g_{m1})$  and  $R_3 = r_{O3} \| (1/g_{m3})$ , we calculate the "gain" from  $V_{DD}$  to  $I_{out}$ . The small-signal gate-source voltage of  $M_4$  equals  $-I_{out}R_3$  and the current through  $r_{O4}$  is  $(V_{DD} - V_X)/r_{O4}$ . Thus,

$$\frac{V_{DD} - V_X}{r_{O4}} + I_{out} R_3 g_{m4} = \frac{V_X}{R_1}.$$

(11.5)

If we denote the equivalent transconductance of  $M_2$  and  $R_S$  by  $G_{m2} = I_{out}/V_X$ , then

$$\frac{I_{Out}}{V_{DD}} = \frac{1}{r_{O4}} \left[ \frac{1}{G_{m2}(r_{O4} || R_1)} - g_{m4} R_3 \right]^{-1}.$$

(11.6)

Note from Chapter 3 that

$$G_{m2} = \frac{g_{m2}r_{O2}}{R_S + r_{O2} + (g_{m2} + g_{mb2})R_Sr_{O2}}.$$

(11.7)

Interestingly, the sensitivity vanishes if  $r_{O4} = \infty$ .

In some applications the supply sensitivity given by (11.6) is prohibitively high. Also, owing to various capacitive paths, the supply sensitivity of the circuit rises at high frequencies.

#### Adding a start-up device

$$I_{out} = \frac{2}{\mu_n C_{ox}(W/L)_N} \cdot \frac{1}{R_S^2} \left( 1 - \frac{1}{\sqrt{K}} \right)^2.$$

(11.4)

- If all transistors in Fig. 11.3 a) carry zero current when the supply is turned on, they may remain off indefinitely because the loop can support a zero current in both branches.

- This is not predicted by (11.4) since we divided by SQRT(I<sub>out</sub>), assuming Iout ≠ 0; The circuit can settle in two different operating conditions. ("start-up" problem)

- Fix: Adding M<sub>5</sub>; path from Vdd through M3 and M1 to ground.

1. februar 2011

#### 11.3 Temperature-independent References

- Little dependence on temperature is essential in many analog circuits.

- If a reference is temperature-independent it is usually process-independent as well.

- Adding two quantities having opposite temperature coefficients ("TCs") displays a zero TC;

$$\alpha_1 \delta V_1 / \delta T + \alpha_2 \alpha_1 \delta V_1 / \delta T = 0$$

Two voltages that have negative and positive TCs must be identified.

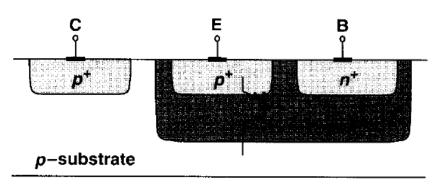

Bipolar devices in CMOS provide well defined TCs.

p-substrate

**Figure 11.10** Realization of a *pnp* bipolar transistor in CMOS technology.

#### Negative TC voltage from pn-junction (11.3.1)

- $I_C = I_s \exp(V_{BE}/V_T)$ ,  $V_T = kT/q$

- $I_S \sim \mu k T n_i^2$

- µ: mobility of carriers

- n<sub>i</sub>: intrinsic ≈ minority carrier concentration of silicon

- Temperature dependency;

μ α μ<sub>0</sub>T<sup>m</sup>, where m ≈ -3/2, and n<sub>i</sub><sup>2</sup> α T<sup>3</sup> exp[-E<sub>g</sub>/(kT)], where E<sub>g</sub> ≈ 1.12 eV is the bandgap energy of silicon.

- $I_S = bT^{4+m} \exp[-E_g/(kT)]$ , b is a proportionality factor.

- $V_{BE} = V_T \ln(I_C / I_S)$

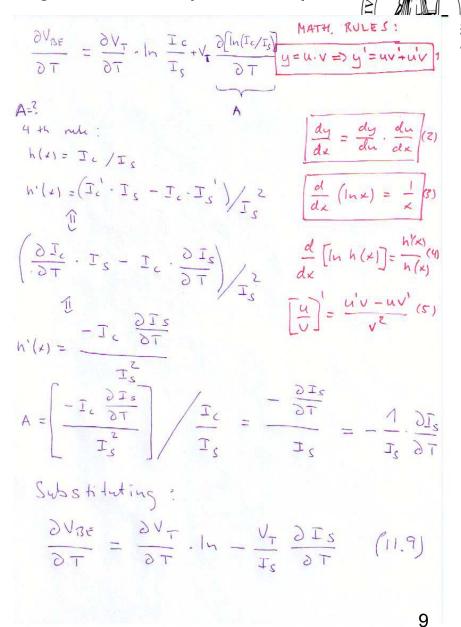

- We can compute the derivative of V<sub>BE</sub> with respect to T. Assume I<sub>C</sub> is constant

test

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_{T}}{\partial T} \ln \frac{I_{C}}{I_{S}} - \frac{V_{T}}{I_{S}} \frac{\partial I_{S}}{\partial T} \qquad (11.9)$$

$$\frac{\partial I_{S}}{\partial T} = b \left( 4+m \right) T^{2+m} \exp \left( -\frac{E_{g}}{kT} \right) + b T^{4+m} \left( \exp \left( -\frac{E_{g}}{kT} \right) + \frac{E_{g}}{kT^{2}} \right)$$

$$A \quad I_{S} = b T^{4+m} \exp \left( -\frac{E_{g}}{kT} \right) + b T^{4+m} \left( \frac{E_{sp}}{kT} \right) + b T^{4+m} \left( \frac{E_{sp}}{kT} \right) = \frac{V_{T}}{kT^{2}} \left( \frac{E_{g}}{kT^{2}} \right)$$

$$= \frac{V_{T}}{V_{T}} \left( \frac{U_{T}m}{T} \right) T^{3+m} + V_{T} T^{4+m} \left( \frac{E_{g}}{kT^{2}} \right) = \frac{U_{T}}{T} \ln \frac{T_{C}}{T} - \frac{U_{T}m}{T} + \frac{U_{T}m}{T} \ln \frac{T_{C}}{T} - \frac{U_{T}m}{T} + \frac{U_{T}m}{T} \ln \frac{T_{C}}{T} - \frac{U_{T}m}{T} \ln \frac{U_{T}m}{T} + \frac{U_{T}m}{T}$$

test

#### Temperature coefficient of $V_{\text{BE}}$ at a given Temperature, T

With the aid of (11.9) and (11.11), we can write

$$\frac{\partial V_{BE}}{\partial T} = \frac{V_T}{T} \ln \frac{I_C}{I_S} - (4+m) \frac{V_T}{T} - \frac{E_g}{kT^2} V_T$$

(11.12)

$$=\frac{V_{BE}-(4+m)V_T-E_g/q}{T}. (11.13)$$

Equation (11.13) gives the temperature coefficient of the base-emitter voltage at a given temperature T, revealing dependence on the magnitude of  $V_{BE}$  itself. With  $V_{BE} \approx 750 \,\text{mV}$  and  $T = 300^{\circ}\text{K}$ ,  $\partial V_{BE}/\partial T \approx -1.5 \,\text{mV/}^{\circ}\text{K}$ .

From (11.13), we note that the temperature coefficient of  $V_{BE}$  itself depends on the temperature, creating error in constant reference generation if the positive-TC quantity exhibits a *constant* temperature coefficient.

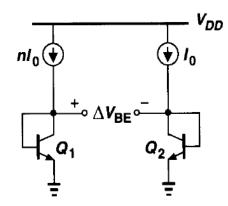

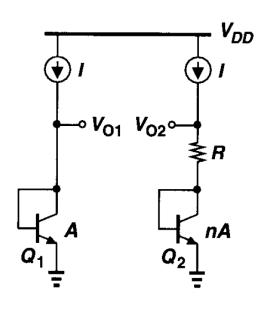

# 11.3.2 Positive-TC Voltage

If two bipolar transistors operate at unequal current densities, the difference between their base-emitter voltages is directly proportional to the absolute temperature Q<sub>1</sub> and Q<sub>2</sub> identical and biased at nI<sub>0</sub> and I<sub>0</sub> AND negligible base currents:

$$\Delta V_{BE} = V_{BE1} - V_{BE2} \tag{11.14}$$

$$= V_T \ln \frac{nI_0}{I_{S1}} - V_T \ln \frac{I_0}{I_{S2}}$$

(11.15)

$$=V_T \ln n. \tag{11.16}$$

Thus, the  $V_{BE}$  difference exhibits a positive temperature coefficient:

$$\frac{\partial \Delta V_{BE}}{\partial T} = \frac{k}{q} \ln n. \tag{11.17}$$

Interestingly, this TC is independent of the temperature or behavior of the collector currents. <sup>1</sup>

**Figure 11.6** Generation of PTAT voltage.

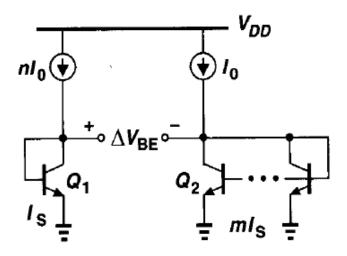

#### Ex. 11.2 Calculating $\Delta V_{BE}$ for the circuit of Fig. 11.7

Figure 11.7

#### **Solution**

Neglecting base currents, we can write

$$= V_T \ln \frac{nI_0}{I_S} - V_T \ln \frac{I_0}{mI_S}$$

$$= V_T \ln(nm).$$

The temperature coefficient is therefore equal to  $(k/q) \ln(nm)$ .

# 11.3.3 Bandgap reference (concept Fig. 11.8 pp. 384)

- Negative and positive TC voltages combined for a reference having a nominally zero temperature coefficient.

- -1.5 mV / degree K at room temp.

- 1.5 / 0.087 = 17.2

- Ln n = 17.2 translates to a prohibitively large n

$V_{REF} = \alpha_1 V_{BE} + \alpha_2 (V_T \ln n)$  • Q<sub>1</sub>: unit transistor, V<sub>01</sub> = V<sub>02</sub>

$\partial V_{BE}/\partial T \approx -1.5 \text{ mV/}^{\circ}\text{K}$  whereas  $\partial V_{T}/\partial T \approx +0.087 \text{ mV/}^{\circ}\text{K}$

#### $\alpha_2 \ln n \approx 17.2$

for zero TC:

$$V_{REF} \approx V_{BE} + 17.2V_T$$

$\approx 1.25 \text{ V}.$

to be equal. Then,  $V_{BE1} = RI + V_{BE2}$  and  $RI = V_{BE1} - V_{BE2} = V_T \ln n$ . Thus,  $V_{O2} = V_{BE2} + V_T \ln n$ , suggesting that  $V_{O2}$  can serve as a temperature-independent reference if  $\ln n \approx 17.2$  (while  $V_{O1}$  and  $V_{O2}$  remain equal).

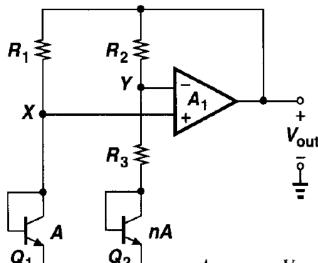

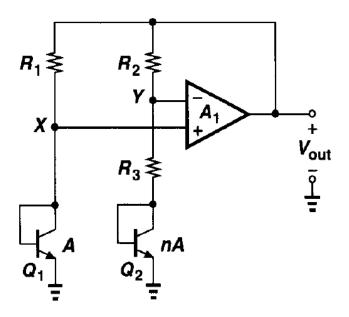

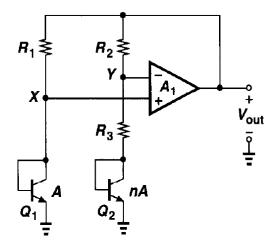

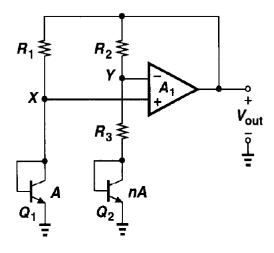

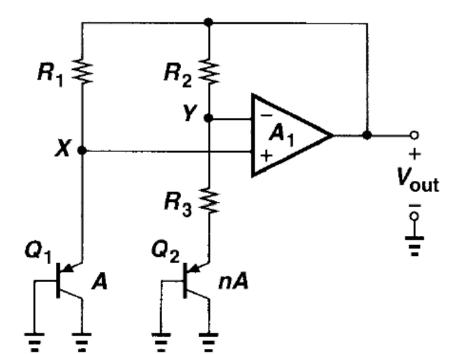

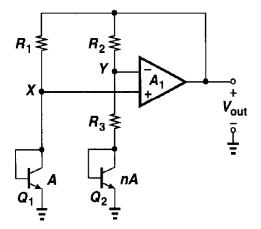

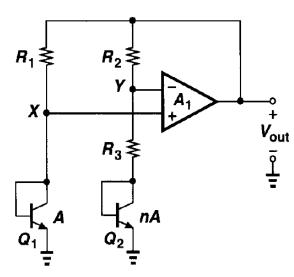

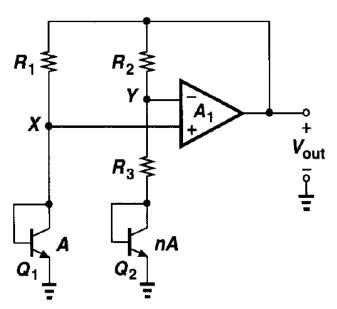

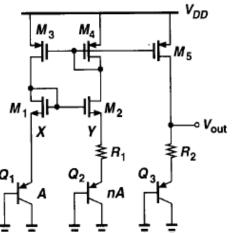

#### Actual Implementation of Bandgap Reference (Fig. 11.9)

$A_1$  senses  $V_X$  and  $V_Y$ , driving the top terminals of  $R_1$  and  $R_2$  ( $R_1 = R_2$ ) such that X and Y settle to approximately equal voltages. The reference voltage is obtained at the output of the amplifier (rather than at node Y). Following the analysis of Fig. 11.8, we have  $V_{BE1} - V_{BE2} = V_T \ln n$ , arriving at a current equal to  $V_T \ln n/R_3$  through the right branch and hence an output voltage of

$$V_{out} = V_{BE2} + \frac{V_T \ln n}{R_3} (R_3 + R_2)$$

(11.22)

$$= V_{BE2} + (V_T \ln n) \left( 1 + \frac{R_2}{R_3} \right). \tag{11.23}$$

For a zero TC, we must have  $(1 + R_2/R_3) \ln n \approx 17.2$ . For example, we may choose n = 31 and  $R_2/R_3 = 4$ . Note these results do not depend on the TC of the resistors.

The circuit of Fig. 11.9 entails a number of design issues. We consider each one below.

#### Design issues for the BG-ref

- Collector Current variation

- Compatibility with CMOS Technology

- Op Amp offset and output impedance

- Feedback Polarity

- Nadgap Reference exhibiting nominally-zero TC is given by a few fundamental numbers

- Supply Dependence and Start-Up

- Curvature Correction

#### Collector Current variation ("issue 1/7")

The circuit in Fig. 11.9 violates the earlier assumption that the collector currents of Q1 and Q2 (given by V<sub>T</sub> In n / R<sub>3</sub>) are proportional to T, whereas

$$\partial V_{BE}/\partial T \approx -1.5 \text{ mV/}^{\circ}\text{K}$$

was derived for a constant current. What happens to the temp. coeff. of  $V_{\text{BE}}$  if the collector currents are PTAT?

iterative solution, let us assume  $I_{C1} = I_{C2} \approx (V_T \ln n)/R_3$ . Returning to Eq. (11.9) and including  $\partial I_C/\partial T$ , we have

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_C}{I_S} + V_T \left( \frac{1}{I_C} \frac{\partial I_C}{\partial T} - \frac{1}{I_S} \frac{\partial I_S}{\partial T} \right). \tag{11.24}$$

Since  $\partial I_C/\partial T \approx (V_T \ln n)/(R_3 T) = I_C/T$ , we can write

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_C}{I_S} + \frac{V_T}{T} - \frac{V_T}{I_S} \frac{\partial I_S}{\partial T}.$$

(11.25)

Equation (11.13) is therefore modified as

$$\frac{\partial V_{BE}}{\partial T} = \frac{V_{BE} - (3+m)V_T - E_g/q}{T},$$

(11.26)

indicating that the TC is slightly less negative than  $-1.5 \text{ mV/}^{\circ}\text{K}$ .

#### Compatibility with CMOS Technology ("issue 2/7")

**Figure 11.10** Realization of a *pnp* bipolar transistor in CMOS technology.

- Derivation of a temperature independent voltage relies on the exponential characteristics of bipolar devices for both negative and positive-TC quantities

- We seek structures in standard CMOS that exhibit such characteristics

- Nwell- process; pnp as depicted

- Other possibilities; pwell- / triple-well / BiCMOS

# BG-reference from Fig. 11.8 implemented with pnp transistors

**Figure 11.10** Realization of a *pnp* bipolar transistor in CMOS technology.

**Figure 11.11** Circuit of Fig. 11.9 implemented with *pnp* transistors.

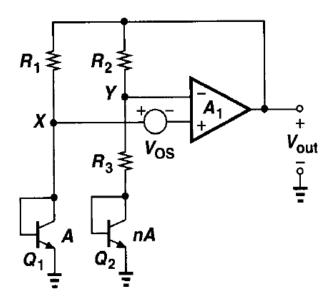

#### Op Amp Offset and Output Impedance ("issue 3/7)

- Vout  $\neq$  0 when Vx = Vy

- The input offset voltage introduces error in the output voltage

- $V_{OS}$  is amplified by 1 +  $R_2$  /  $R_3$  (eq. 11.28)

- V<sub>OS</sub> varies with temperature (chapter 13)

- Reduce offset by using large devices in a carefully chosen topology (chapter 18).

troduces error in the output voltage. Included in Fig. 11.12, the effect is quantified as  $V_{BE1} - V_{OS} \approx V_{BE2} + R_3 I_{C2}$  (if  $A_1$  is large) and  $V_{out} = V_{BE2} + (R_3 + R_2) I_{C2}$ . Thus,

$$V_{out} = V_{BE2} + (R_3 + R_2) \frac{V_{BE1} - V_{BE2} - V_{OS}}{R_3}$$

(11.27)

$$= V_{BE2} + \left(1 + \frac{R_2}{R_3}\right) (V_T \ln n - V_{OS}), \tag{11.28}$$

### Feedback Polarity ("issue 4/7")

Feedback Polarity

**Feedback Polarity** In the circuit of Fig. 11.9, the feedback signal produced by the op amp returns to both of its inputs. The negative feedback factor is given by

$$\beta_N = \frac{1/g_{m2} + R_3}{1/g_{m2} + R_3 + R_2},\tag{11.31}$$

and the positive feedback factor by

$$\beta_P = \frac{1/g_{m1}}{1/g_{m1} + R_1}. (11.32)$$

To ensure an overall negative feedback,  $\beta_P$  must be less than  $\beta_N$ , preferably by roughly a factor of two so that the circuit's transient response remains well-behaved with large capacitive loads.

# Bandgap Reference ("issue 5/7") producing a reference voltage based on the bandgap voltage of silicon ( $E_q/q$ )

$$V_{REF} \approx V_{BE} + 17.2V_T \tag{11.20}$$

$$\approx 1.25 \text{ V}.$$

(11.21)

**Bandgap Reference** The voltage generated according to (11.20) is called a "bandgap reference." To understand the origin of this terminology, let us write the output voltage as

$$V_{REF} = V_{BE} + V_T \ln n \tag{11.33}$$

and hence:

$$\frac{\partial V_{REF}}{\partial T} = \frac{\partial V_{BE}}{\partial T} + \frac{V_T}{T} \ln n. \tag{11.34}$$

Setting this to zero and substituting for  $\partial V_{BE}/\partial T$  from (11.13), we have

$$\frac{V_{BE} - (4+m)V_T - E_g/q}{T} = -\frac{V_T}{T} \ln n. \tag{11.35}$$

If  $V_T \ln n$  is found from this equation and inserted in (11.33), we obtain:

$$V_{REF} = \frac{E_g}{q} + (4+m)V_T. {(11.36)}$$

Thus, the reference voltage exhibiting a nominally-zero TC is given by a few fundamental numbers: the bandgap voltage of silicon,  $E_g/q$ , the temperature exponent of mobility, m, and the thermal voltage,  $V_T$ . The term "bandgap" is used here because as  $T \to 0$ ,  $V_{REF} \to E_g/q$ .

### Supply Dependence and Start-Up ("issue 6/7")

- The output voltage is relatively independent of V<sub>dd</sub> as long as the open loop gain (A<sub>OL</sub> = V<sub>out</sub>/(V<sup>+</sup> V<sup>-</sup>)) of the op amp is sufficiently high.

- A start-up mechanism may be required because if V<sub>x</sub> and V<sub>y</sub> are equal to zero, the differential input pair of the op amp may turn off.

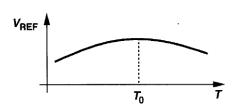

#### Curvature correction ("issue 7/7")

**Figure 11.16** Curvature in temperature dependence of a bandgap voltage.

Figure 4 Output reference Verf vs. temperature.

- The TC is typically zero at one temperature and positive or negative at others (due to temperature variation of base emitter voltages, collector currents and offset voltages).

- Curvature correction techniques are seldom used in CMOS (but used in bipolar impl.) due to offset- and process variations from sample to sample.

**Figure 11.17** Variation of the zero-TC temperature for difference samples.

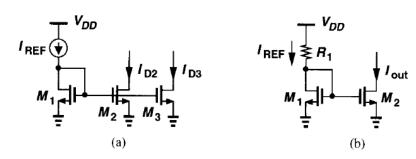

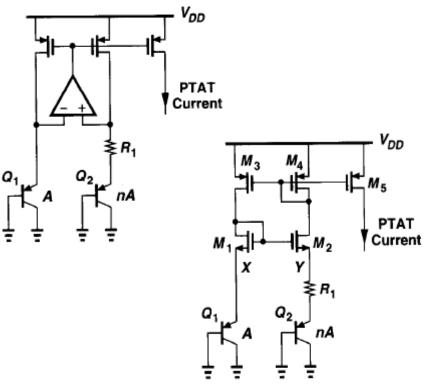

#### 11.4 PTAT Current Generation (Fig. 11.18-11.20)

- \* The bias currents of the bipolar transistors are proportional to absolute temperature.

- \* Fig. 11.19:  $M_1$ - $M_2$  and  $M_3$ - $M_4$  are identical pairs, to ensure  $V_x = V_Y \rightarrow I_{D1} = I_{D2} = V_T \ln n / R_1$

- The circuit in 11.19 may be modified to provide a BG-ref voltage as well (Fig. 11.20).

- Fig. 11.20

$$V_{REF} = V_{BE3} + \frac{R_2}{R_1} V_T \ln n, \tag{11.37}$$

#### Constant Gm-biasing (11.5)

A simple circuit used to define the transconductance is the supply-independent bias topology of Fig. 11.3. Recall that the bias current is given by

$$I_{out} = \frac{2}{\mu_n C_{ox}(W/L)_N} \frac{1}{R_S^2} \left( 1 - \frac{1}{\sqrt{K}} \right)^2.$$

(11.38)

Thus, the transconductance of  $M_1$  equals

$$g_{m1} = \sqrt{2\mu_n C_{ox} \left(\frac{W}{L}\right)_N I_{D1}} \tag{11.39}$$

$$=\frac{2}{R_S}\left(1-\frac{1}{\sqrt{K}}\right),\tag{11.40}$$

- Often desirable to bias transistors so that noise, small signal gain and speed is not affected by transconductance variations

- Transconductance may be defined by the topology from Fig. 11.3

- In real life, R<sub>S</sub> does vary with temperature and process.

- If the temperature coefficient of the resistor is known, bandgap and PTAT reference generation techniques can be utilized to cancel the temperature dependence. Process variations, however, limit the accuracy with which the transconductance is defined.

- If having a precise clock → SC impl.

#### Constant Gm-biasing by Switched Capacitor "resistor"

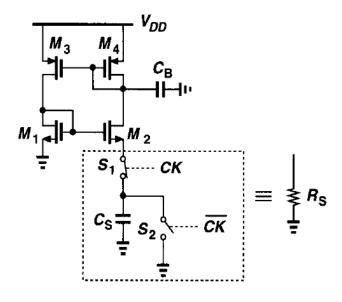

**Figure 11.21** Constant- $G_m$  biasing by means of a switched-capacitor "resistor."

- Precise clock frequency must be available

- Change R with Switched Capacitor ("SC") equivalent

- May give more compact realization

test 27

## Outline – Tuesday, February 1st

- 11.1 General considerations

- 11.2 Supply-independent biasing

- 11.3 Temperature-independent References 2.46540

- 11.3.1 Negative TC-voltage

- 11.3.2 Positive TC-voltage

- 11.3.3 Bandgap reference

- 11.4 PTAT Current generation

- 11.5 Constant-Gm Biasing (?)

- 12.2 Sampling Switches

- 12.3 Switched Capacitor amplifiers (?)

Figure 4 Output reference Verf vs. temperature.

Figure 5 Output reference Vref vs. power supply Vdd.

A High Precision Curvature Compensated Bandgap Reference without Resistors

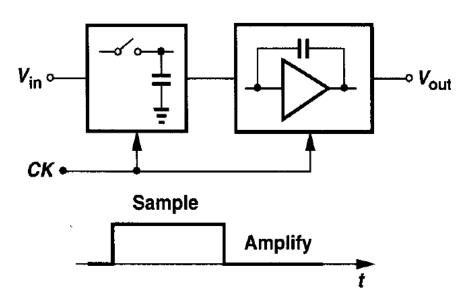

#### Introduction to Switched Cap. Circuits (ch. 12 in "Razavi")

**Figure 12.7** General view of switched-capacitor amplifier.

- Continous time processing, examples: audio, video, analog systems.

- \*\*Yout \* "Sample-data / discrete time";

The input is sampled at periodic instants of time, ignoring its value at other times. The circuit then processes each "sample" producing a valid output at the end of each period.

- Switched capaitor circuits are used in filters, comparators, ADCs and DACs.

#### MOSFETs as switches (ch. 12.2 in "Razavi")

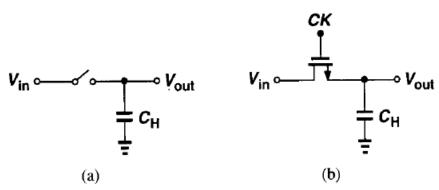

Figure 12.8 (a) Simple sampling circuit, (b) implementation of the switch by a MOS device.

- Nice properties of MOS transistors as switches;

- Can be on while carrying zero current

The source and drain need not follow the gate voltage (not the case with bipolar transistors, typically necessitating complex bipolar circuits for sampling)

Used widely in SC-filters, Sample-and-Hold circuits, ADCs and DACs (both Nyquist and oversampling converters)

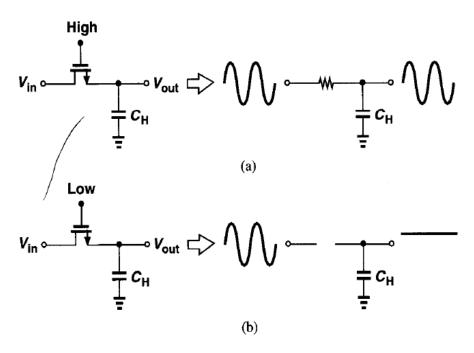

# Track (/sample-) and Hold capabilities of a sampling circuit

12.2 in "Razavi")

Nice properties of MOS

Figure 12.10 Track and hold capabilities of a sampling circuit.

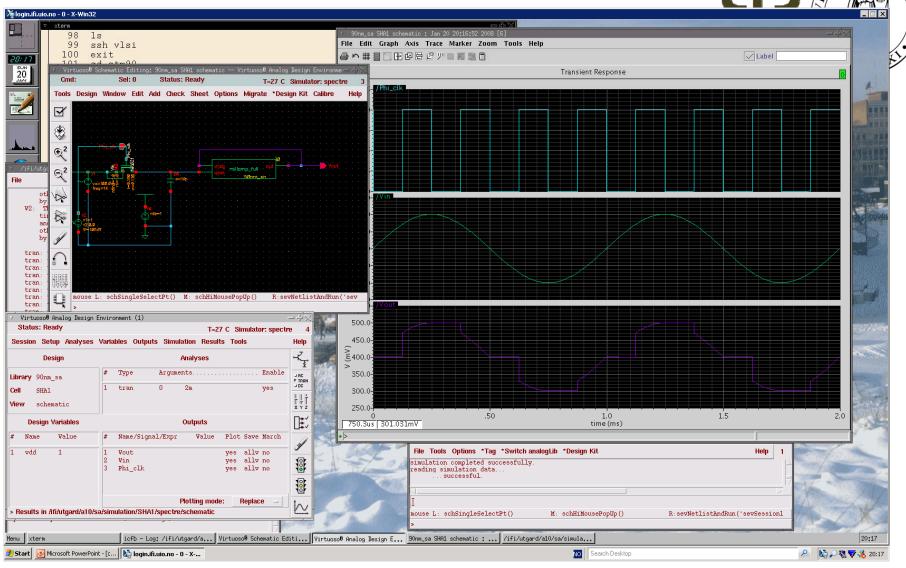

Schematic entry and simulations in Cadence

#### Next week:

- Sample and Hold circuits, Data converter fundamentals

- Messages are given on the INF4420 homepage.

- Questions: <a href="mailto:sa@ifi.uio.no">sa@ifi.uio.no</a>, 22852703 / 90013264