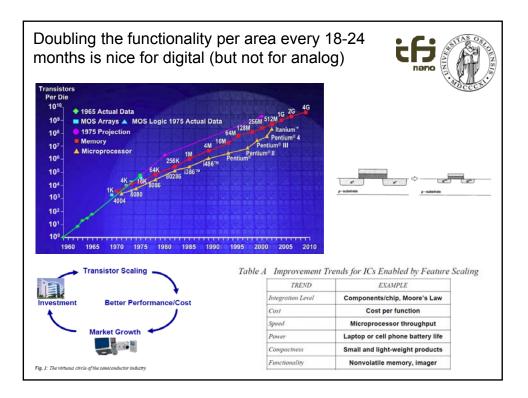

| Scaling and digital circuits                                                                                                                                                                                                              |                                                                                                  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| $I_{D,scaled} = \frac{1}{2} \mu_n (\alpha C_{ox}) \left( \frac{W/\alpha}{L/\alpha} \right) \left( \frac{V_{GS}}{\alpha} - \frac{V_{TH}}{\alpha} \right)^2$ $= \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 \frac{1}{\alpha},$ | <ul> <li>Current capability drops by<br/>1/α (α≈1/0.7)</li> </ul>                                |  |

| $C_{ch,scaled} = \frac{W}{\alpha} \frac{L}{\alpha} (\alpha C_{ax})$ $= \frac{1}{\alpha} WLC_{ax}.$ $F = \frac{1}{\alpha} WLC_{ax}.$ $F = \frac{1}{\alpha} WLC_{ax}.$                                                                      | <ul> <li>Capacitances decrease by<br/>the scaling factor, 1/α</li> </ul>                         |  |

| Figure 16.2 Soling of SD pacton capertances.                                                                                                                                                                                              | <ul> <li>Delay decreases by 1/α</li> </ul>                                                       |  |

| $C_{S/D,scaled} = \frac{W}{\alpha} \frac{E}{\alpha} (\alpha C_j) + 2\left(\frac{W}{\alpha} + \frac{E}{\alpha}\right) (C_{jrw})$ $= [WEC_j + 2(W + E)C_{jrw}] \frac{1}{\alpha}.$                                                           | <ul> <li>Number of transistors per<br/>area scales by α<sup>2</sup>.</li> </ul>                  |  |

| $T_{d,scaled} = \frac{C/\alpha}{I/\alpha} \frac{V_{DD}}{\alpha}$ $= \left(\frac{C}{I} V_{DD}\right) \frac{1}{\alpha}.$                                                                                                                    | <ul> <li>The reduction of power<br/>and delay and the<br/>increase in circuit density</li> </ul> |  |

|                                                                                                                                                                                                                                           | make scaling extremely<br>attractive for digital<br>systems. 18                                  |  |

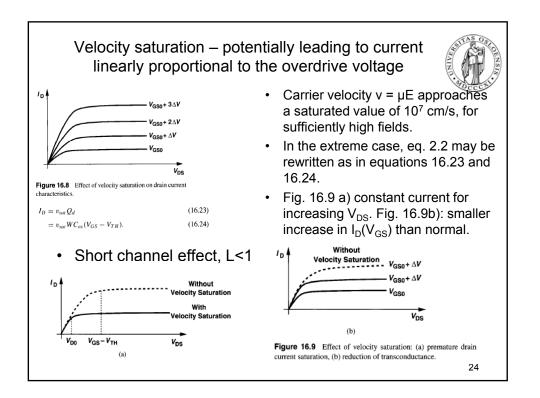

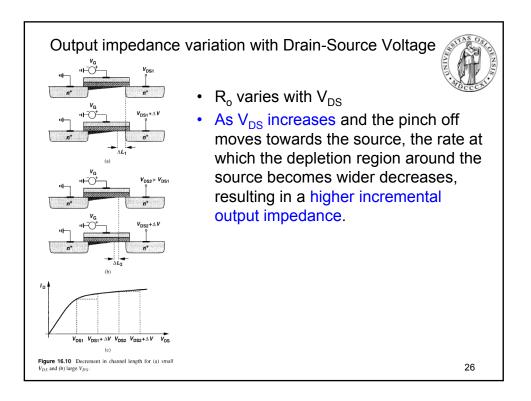

| Short channel effe                                                                                                                                                                                                                                                                                                                                                                        | ects (L < 3 um)                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>The electric fields tend to increase because the supply voltage has not scaled proportionally.</li> <li>The built-in potential term in eq. 16.5 is neither scalable nor negligible</li> <li>The depth of the S/D junctions cannot be reduced easily</li> <li>The mobility decreases as the substrate doping increases</li> <li>The subthreshold slope is not scalable</li> </ul> | Threshold voltage variation (Ch.<br>16.2.1)<br>Mobility degradation with<br>Vertical field (Ch. 16.2.2)<br>Velocity saturation (Ch. 16.2.3)<br>Hot carrier effects (Ch. 16.2.4)<br>Output impedance variation with<br>Drain-Source voltage (Ch.<br>16.2.5) |

| $W_d = \sqrt{\frac{2\epsilon_{si}}{q}} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)(\phi_B + V_R),\tag{16.5}$                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                         |