# UiO **Department of Informatics**

University of Oslo

### **IN4180 - Analog Microelectronics Design**

### **Biasing, References and Regulators - pt 1**

Kristian G. Kjelgård

University of Oslo

University of Oslo

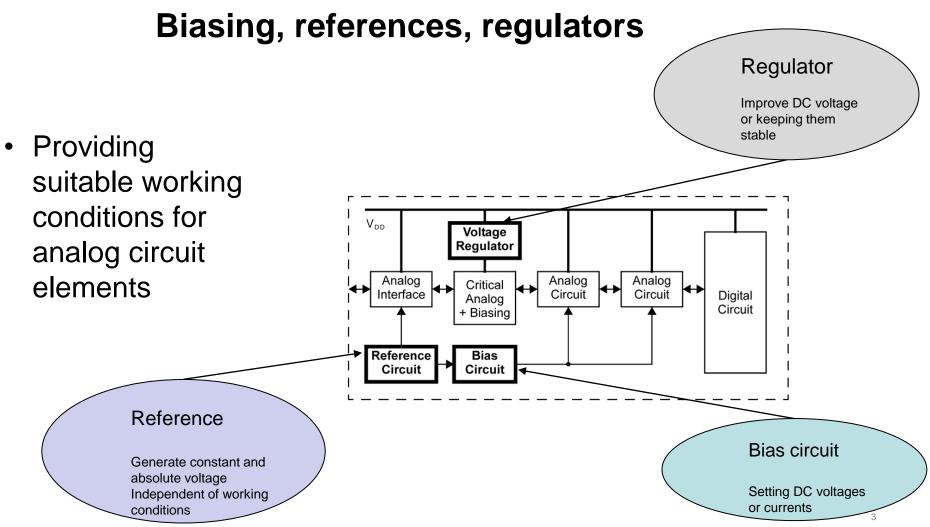

# Biasing

UiO **Department of Informatics** University of Oslo

# **Bias circuits**

- What bias voltage Vb?

- Constant drain current in match diff-pair?

- Constant voltage drop over R?

- Constant gain?

Assuming 10-20% device variations

# **Bias circuits**

- Provide a bias voltage that tracks varying parameters and sets operation point accordingly

- Stable Gm In may cases the most important

- Compensate supply voltage, temperature and process

variations

UiO **Department of Informatics** University of Oslo

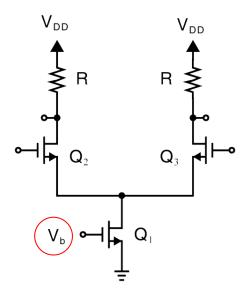

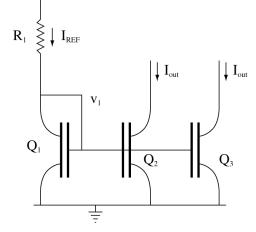

Crude "Bias"

$$\Delta I_{out} = \frac{\Delta V_{DD}}{R_1 + 1/g_{m1}} \cdot \frac{(W/L)_2}{(W/L)_1}$$

- Resistive current generator

- Known load  $\rightarrow$  good approximation

- Sensitivite to Vdd and process parameters

University of Oslo

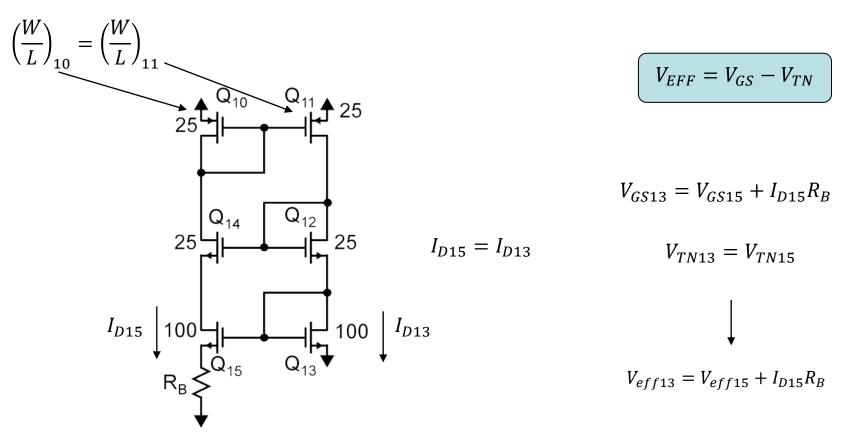

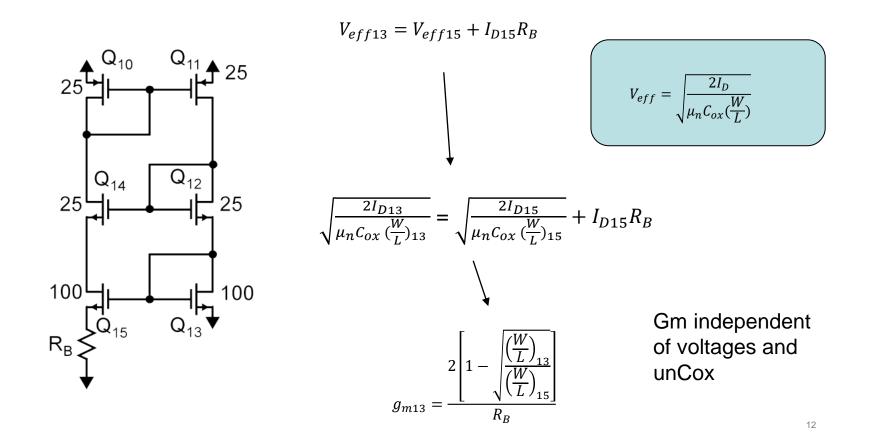

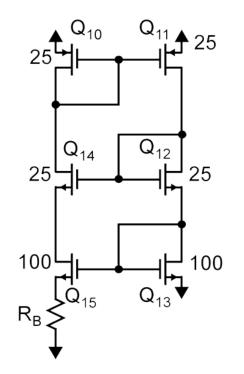

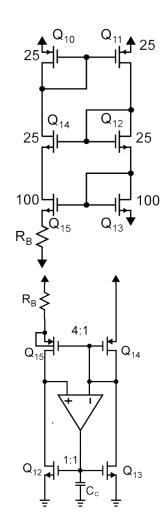

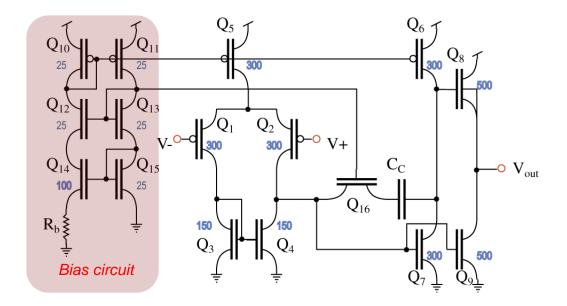

## **Constant transconductance bias circuit**

## **Constant transconductance bias circuit**

## **Constant transconductance bias circuit**

For the special case:

$$\left(\frac{W}{L}\right)_{15} = 4\left(\frac{W}{L}\right)_{13} \Rightarrow \qquad g_{m13} = \frac{1}{R_B}$$

UiO **Contemportation Department of Informatics** University of Oslo

## **Constant transconductance**

PMOS devices

$$g_{mp} = \sqrt{\frac{\mu_p}{\mu_n} \frac{\left(\frac{W}{L}\right) I_D}{\left(\frac{W}{L}\right) I_{15}}} \approx g_{m13}$$

- Unfortunately, mobility variations are significant

- Additional compensation for

- Temp, body ...

- Second stable state (I = 0)

- Startup circuits required

- Runaway compensation at high temp. High power consumption

University of Oslo

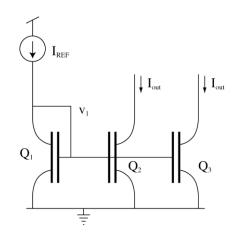

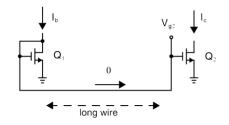

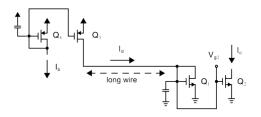

# **Bias distribution**

- Provide Vb -> transistors independent of temperature, process and supply parameters

- May be large and should be reused by several sub-circuits

#### Voltage mode distribution

- Vtn variation sensitive

- GND potential sensitive

- Noise at high Z nodes

- Low current consumption

#### Current mode distribution

- Vtn independent

- GND indepentent

- More devices required

- Higher current consumption + Id

University of Oslo

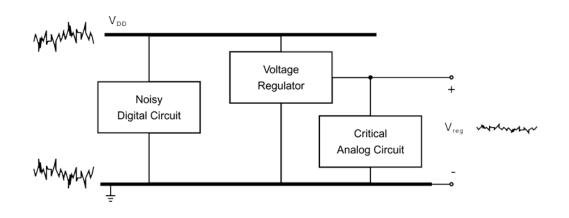

# **Voltage Regulator**

University of Oslo

- Handle VDD variations

- Provide power (in contrary to bias / references)

- Reduce supply voltage

- Stabilize supply voltage for improved performance

- Filter noisy supply

- Ground ref may still convey noise

University of Oslo

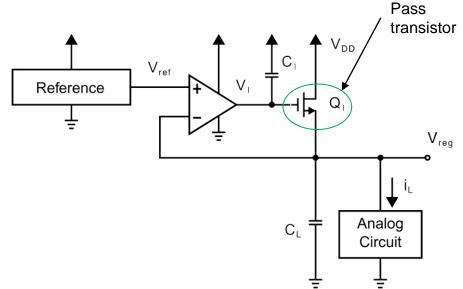

# Classic linear regulator implementation

- Quiet and stable on-chip voltage

- Input reference

- Amp gain

- Specifications

- Power-supply rejection ratio

$PSSR(\omega) = 10 \log_{10} \left( \frac{v_{DD}}{v_{reg}} \right)$

- Output impedance

- Transient current load

- Dropout voltage

- Minimum voltage between supply and regulated voltage

UiO **Contemportation Department of Informatics** University of Oslo

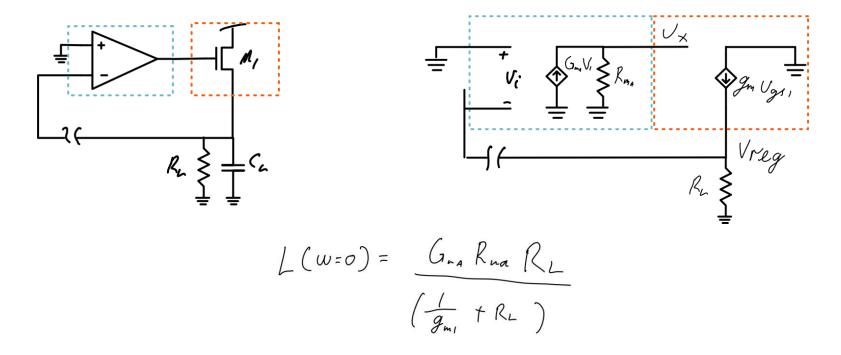

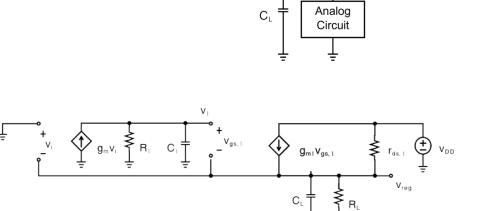

## Regulator Feedback analysis – DC ( $\omega$ =0)

UiO **Department of Informatics**

University of Oslo

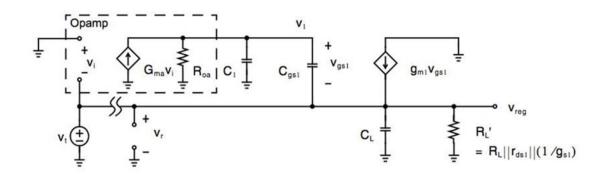

## **Regulator Feedback analysis AC**

$$L(S) = \left(\frac{G_{m_A} R_{o_A} R_L}{R_L + \frac{1}{g_{m_I}}}\right) \frac{\left(1 + \frac{S}{w_z}\right)}{\left(1 + \frac{S}{w_{p_I}}\right)\left(1 + \frac{S}{w_{p_I}}\right)}$$

University of Oslo

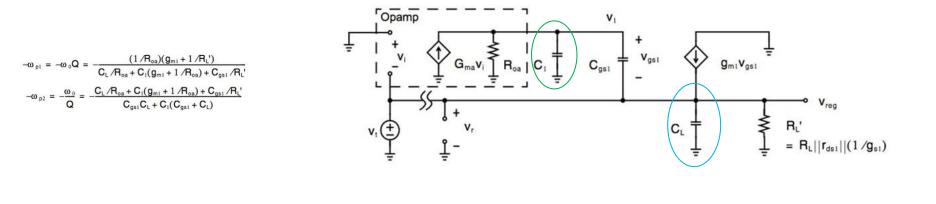

## **Regulator Feedback analysis AC poles**

As a designer make  $C_1$  large Dominant pole  $\mathcal{W}_{P1} \approx \mathcal{R}_{oq} \subset \mathcal{I}$  $\mathcal{W}_{P2} \approx \mathcal{H}_{m'}$  $\mathcal{W}_{P2} \approx \mathcal{H}_{m'}$  UiO **Department of Informatics** University of Oslo

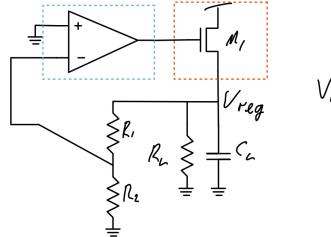

# Low Drop-out regulator

- Dropout voltage

- Maximum regulated voltage

- pMOS for minimal voltage drop

- Notice reversed amp polarity

- Regulating loop

$$L(s) = \frac{G_{ma}R_{oa}g_{m}R'_{L}}{\left(1 + \frac{s}{\omega_{pa}}\right)\left(1 + \frac{s}{\omega_{pL}}\right)}$$

• Amp pole

$\omega_{pa} = \frac{1}{R_{oa}C_1'}$

$V_{DD}$

$V_{\perp}$

$V_{\text{ref}}$

Reference

Ť

pMOS pass

transistor

$V_{reg}$

- Amp pole dominant  $\rightarrow$  worse rejection

- Output pole  $\omega_{pL} =$

$$P_{pL} = \frac{1}{R'_L C_L}$$

$$C_1' = C_1 + C_{gs1}$$

23

# **Regulator design considerations**

- NMOS pass transistor -> better PSRR

- NMOS pass needs Vgs > Vth... Not suitable for Low Dropout

- PMOS pass transistor -> only limited by Veff (need some channel to get current trough

- High W needed with low VDD -Vreg)

- Higher gain in last stage (CS) and VDD is source voltage -> poorer PSRR

UiO **Contemportation Department of Informatics** University of Oslo

## **Regulator voltage control**

$$V_{reg} = V_{ref} \left( 1 + \frac{R_1}{R_2} \right)$$