## INF2270, building a simple memory control unit: example solution

February 17, 2012

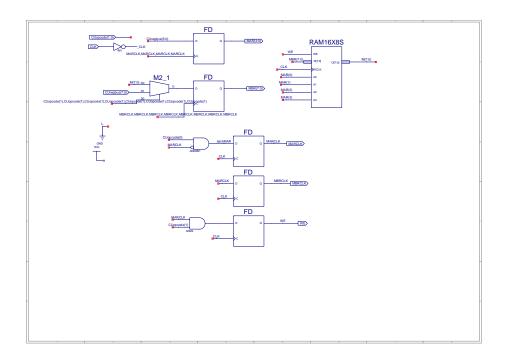

Figure 1 shows the solution. The combinational logic circuits resulting from the state transition conditions have been added to the D-flipflop input:

$MARCLK \le CUopcode(0) \land \overline{MARCLK}$

MBRCLK <= MARCLK

$WE \ <= \ CUopcode(1) \land MARCLK$

This implements the state machine as defined in the exercise's figure 1.

The following control signals were not yet connected in top.sch: The control signal for the bus multiplexer is directly 'CUopcode(1)' setting the source of the MBR to the CUregbus, if CUopcode(1) is low and to the memory output 'M' if opcode(1) is high. The clock signals for the MAR and MBR are (obviously) MARCLK and MBRCLK respectively, latching MAR at the start of the first clock cycle and MBR at the start of the second.

Figure 1: Schematics of the solution