# INF2270, example solution: more detailed pipelining speed-up and a counter with synchronous load

March 19, 2012

### Pipelined Processor Absolute Speed-Up

#### Part 1:

- 1.  $\frac{1\text{GHz}}{4\text{CPI}} = 250\text{MIPS}$

- 2.  $\frac{900MHz}{1.2CPI} = 750MIPS$

#### Part 2:

- 1. 1/259ps=3.86GHz3.86GIPS  $\frac{3.86GIPS}{250MIPS} = 15.44$  times faster

- $\begin{array}{l} 2. \ \, \frac{3.86 \mathrm{GHz}}{1.2 \mathrm{CPI}} = 3.22 \mathrm{GIPS} \\ \frac{3.22 \mathrm{GIPS}}{250 \mathrm{MIPS}} = 12.88 \ \mathrm{times \ faster} \end{array}$

- 3.  $\frac{3980ps}{\frac{1}{269ps}} + 20ps = 269ps$  $\frac{1}{269ps} = 3.72GHz$  $\frac{3.72GHz}{1.2CPI} = 3.10GIPS$

## Synchronous Counter with load

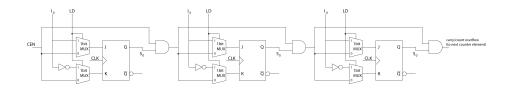

Figure 1 shows one possible solution. Remember that a JK flipflop works like a T-flipflop if J and K are shortened. This is the case if LD=0 since the same signal is routed to both J and K through the multiplexers and the circuit becomes equivalent to the synchronous counter without a LD control signal.

When LD=1, on the other hand, K receives the inverted J signal and J is shorted to the input. Thus, on the next clock edge, the value I is loaded into the counter.

Figure 1: A counter with LD and CE control signals