## INF3410/4411, Fall 2018

Philipp Häfliger hafliger@ifi.uio.no

Excerpt of Sedra/Smith Chapter 15: Inverter Delay

▲□▶ ▲圖▶ ▲臣▶ ★臣▶ ―臣 …の�?

### Content

Digital/Binary and Analog Linear/Small-Signal Abstraction

・ロト ・ 日 ・ ・ 日 ・ ・ 日 ・ ・ つ へ ()

Logic gates (book 15.1)

#### Digital/Binary and Analog Linear/Small-Signal Abstraction A digital MOSFET model

Logic gates (book 15.1)

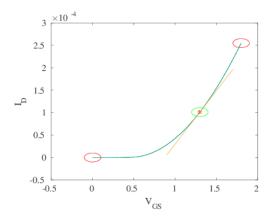

Digital and Analog Simplifications i<sub>D</sub> vs. v<sub>GS</sub>

The transistor level digital abstraction only considers the binary input range  $v_{GS} \in \{0, Vdd\}$ The transistor level analog abstraction (small signal model) only considers a small input range around a bias point/point of

operation and linear output approximation.

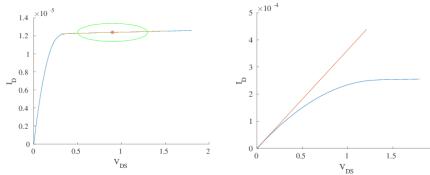

## Digital and Analog Simplifications i<sub>D</sub> vs. v<sub>DS</sub>

Again the transistor level analog abstraction only considers a small input range around a bias point/point of operation and linear output approximation. In the active region the linear approximation holds for quite a large range for  $v_{DS}$ .

The transistor level digital abstraction also uses a linear approximation here for the two different  $v_{GS}$ : an open circuit and a resitive behaviour  $R_{on} = r_{ds}$ .

2

# Digital MOSFET Model Variant

Thus in the digital transistor abstraction both pFET and nFET have two conductive states controlled by the input voltage at the gate.

・ロッ ・雪 ・ ・ ヨ ・ ・

э

#### Digital/Binary and Analog Linear/Small-Signal Abstraction

#### Logic gates (book 15.1)

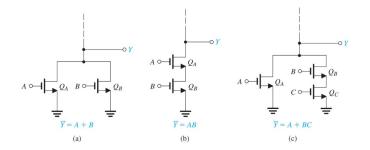

## Pull-Up and Pull-Down

Logic functions can be implemented by complementary pull-up and pull down networks ... or you can just add a resistor tot PUN or PDN... Would that be smart?

◆□▶ ◆□▶ ◆□▶ ◆□▶ ● ● ●

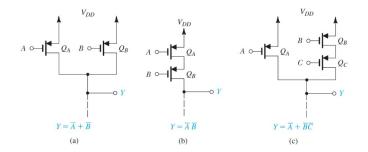

#### **PDN** examples

◆ロト ◆昼 ▶ ◆臣 ▶ ◆臣 ▶ ● 臣 ● の Q (2)

### **PUN** examples

イロト 不得下 不同下 不同下

æ

Usually, logic gates are composed of a PUN and PDN that implement eachothers *inverse* function. Such that always either the PUN or the PDN are active. E.g. the PDN:

$$\bar{Y} = (A+B) * C$$

And the PUN

$$Y = \overline{(A+B) * C} = \dots$$

・ロト ・ 日 ・ ・ 日 ・ ・ 日 ・ ・ つ へ ()

Usually, logic gates are composed of a PUN and PDN that implement eachothers *inverse* function. Such that always either the PUN or the PDN are active. E.g. the PDN:

$$\bar{Y} = (A+B) * C$$

And the PUN

$$Y = \overline{(A+B)*C} = \overline{(A+B)} + \overline{C} = (\overline{A}*\overline{B}) + \overline{C}$$

・ロト ・ 日 ・ ・ 日 ・ ・ 日 ・ ・ つ へ ()

#### Digital/Binary and Analog Linear/Small-Signal Abstraction

Logic gates (book 15.1)

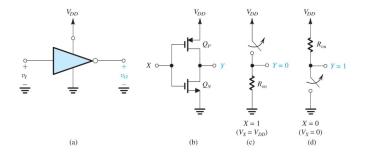

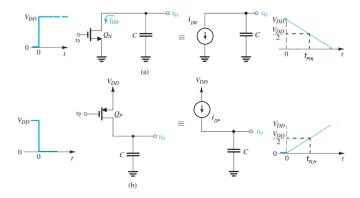

## **CMOS** Inverter Model

◆□ > ◆□ > ◆豆 > ◆豆 > ̄豆 = のへで

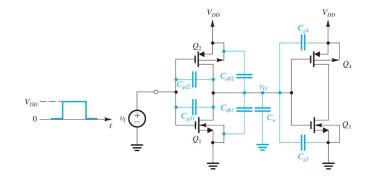

### CMOS Inverter HF Model

$C = 2 * (C_{gd1} + C_{gd2}) + C_{db1} + C_{db2} + C_{g3} + C_{g4} + C_W$ (15.59)

ヘロト ヘアト ヘヨト ヘ

**∃** ⊳

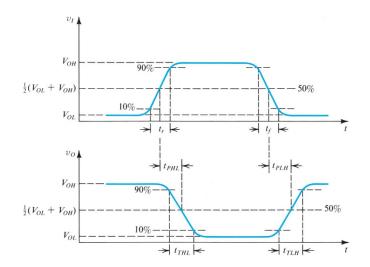

# Propagation delay and transition time

▲□▶ ▲□▶ ▲□▶ ▲□▶ ▲□ ● ● ●

# IC model for delay

$$\hat{i}_{DN} = \frac{i_{DN}(Vdd) + i_{DN}(\frac{Vdd}{2})}{2}$$

(15.47)

$$t_{PHL(LH)} = \frac{CVdd}{2\hat{i}_{DN(DP)}} = \frac{\alpha_{n(p)}C}{k_{n(p)}Vdd}$$

(15.46, 15.50)

◆□▶ ◆□▶ ◆三▶ ◆三▶ ●□ ● ●

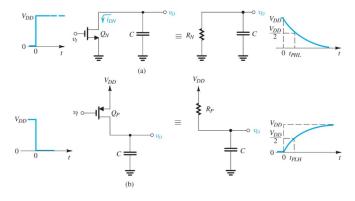

## RC model for delay

$$R_{N(P)} = \frac{12.5(30)}{(W/L)_{n(P)}} k\Omega$$

(15.56)

$t_{PHL(LH)} = 0.69 R_{n(p)} C$  (15.54)

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへで

### Observations

- To balance t<sub>PHL</sub> and t<sub>PLH</sub> often pFETs in digital circuits are chosen to be wider than nFETs

- ▶ In contrast to analog circuits, here maximizing speet  $(f_T)$  is prefered before maximizing gain  $(A_0)$ , i.e. digital transistors are most often minimum length. However, small gain still has a negative impact on noise margin.

- These models are really crude and only give an idea of which parameters to tweak in which direction for an expected result. For reasonable absolute estimates one needs to consult transistor level simulation at least, or even post-layout simulation.